# Multi bunch instabilities and cures at the SLS

M. Dehler, P. Pollet, R. Kramert, G. Marinkovic, T. Schilcher (PSI) D. Bulfone, M. Lonza (ELETTRA)

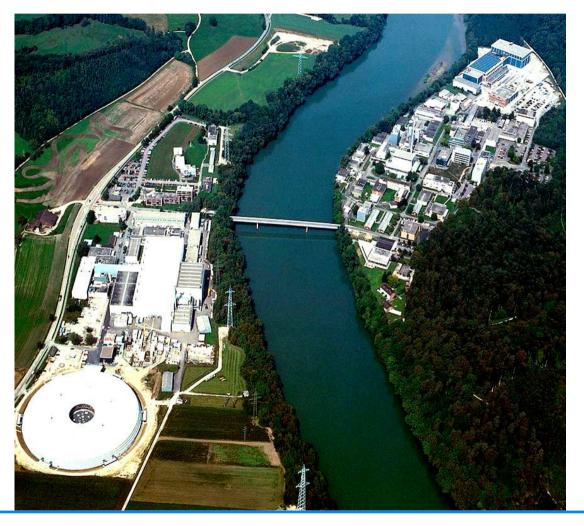

### Aerial view of PSI

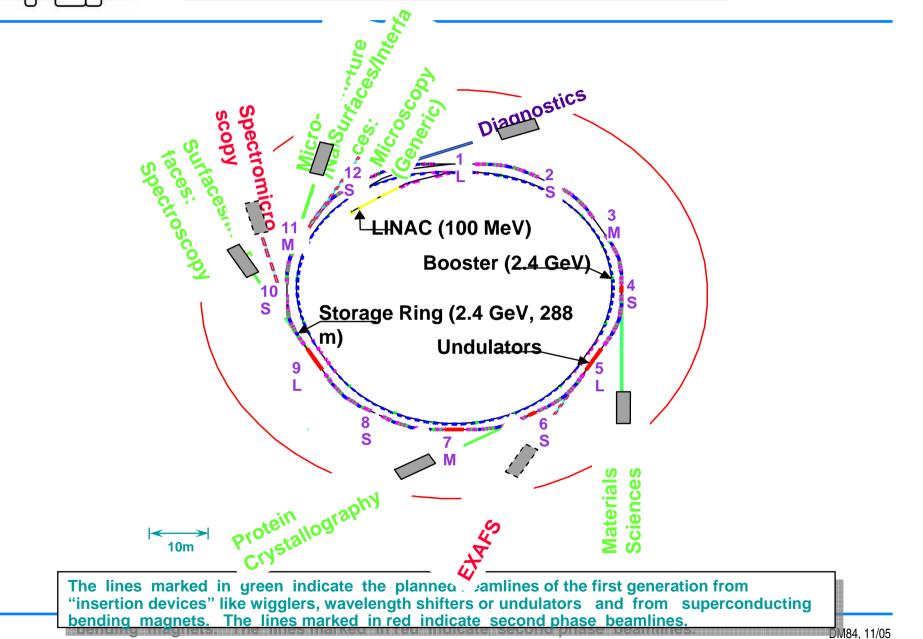

#### **SLS - BEAMLINES**

## (Historical) Overview

| Feedback Parameters                                  |                |                |

|------------------------------------------------------|----------------|----------------|

| General:                                             | Vert.          | Hor.           |

| Tune v                                               | 7.08           | 20.82          |

| Damping time $\tau_{nat}$                            | 9.0 ms         | 9.0 ms         |

| Driving Impedances (max)                             |                |                |

| Resistive Wall                                       | 0.9 MΩ/m       | 0.06 MΩ/m      |

| Cavity HOM                                           | 45 MΩ/m        | 45 MΩ/m        |

| Filter type                                          | 2-tap          | 2-tap          |

| Eff. damping time                                    | 9µs            | 48µs           |

| Max. stable impedance                                | $105M\Omega/m$ | $107M\Omega/m$ |

| Kicker parameters:                                   |                |                |

| Strength $R_s = V_{\parallel}^2/2P$                  | 20.0KΩ         | $14.5K\Omega$  |

| Kick $(\delta \hat{x} = 55 \mu m)$                   | 2800V          | 2400V          |

| Input power per port ( $\delta \hat{x} = 55 \mu m$ ) | 200W           | 200W           |

| Capture Limit for spec. max. power                   |                |                |

| (Only resistive wall)                                | 6.4 <i>mm</i>  | 94 <i>mm</i>   |

| Noise sensistivity:                                  |                |                |

| Noise source: RF FE/ADC                              |                |                |

| $\delta x_{rms}(generated)/\delta x_{rms}(measured)$ | 0.2            | 0.07           |

| Noise source: DAC/PA                                 |                |                |

| (-40 dB Noise assumed.)                              | 0.15µm         | 0.07 <i>µm</i> |

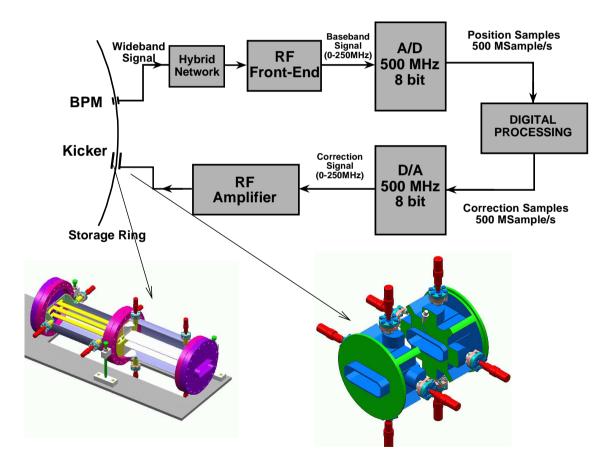

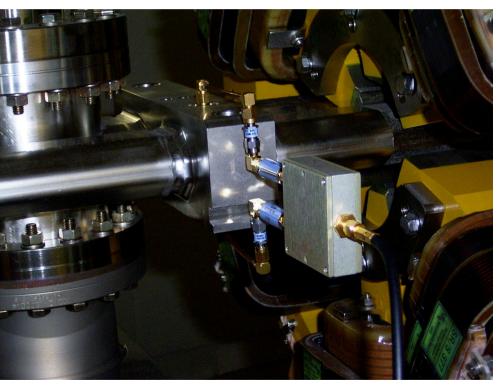

## H/V pickups with hybrids

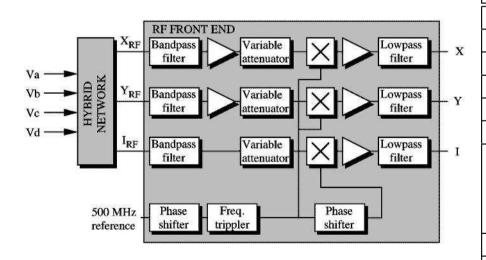

## **RF front end**

| Parameter                 | Specification              |

|---------------------------|----------------------------|

| Center frequency          | 1.5 GHz                    |

| X,Y input signal range    | -49 dBm to -29 dBm         |

| I input signal range      | -23 dBm to -3 dBm          |

| X,Y channel noise figure  | 5 dB at -49 dBm input      |

| Output spectrum window    | 40 kHz to 250 MHz          |

| Max output level          | 1 Vp-p or +4 dBm at 50 ohm |

| Overall bandwidth         |                            |

| 1 dB                      | 250 MHz                    |

| 3 dB                      | 300 MHz                    |

| 20 dB                     | 400 MHz                    |

| Phase shift control range | > 430 degrees at 1.5 GHz   |

| Gain control range        | 20 dB                      |

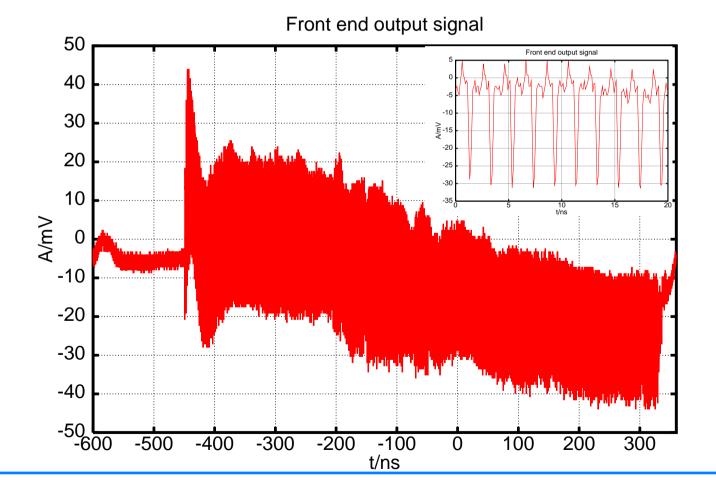

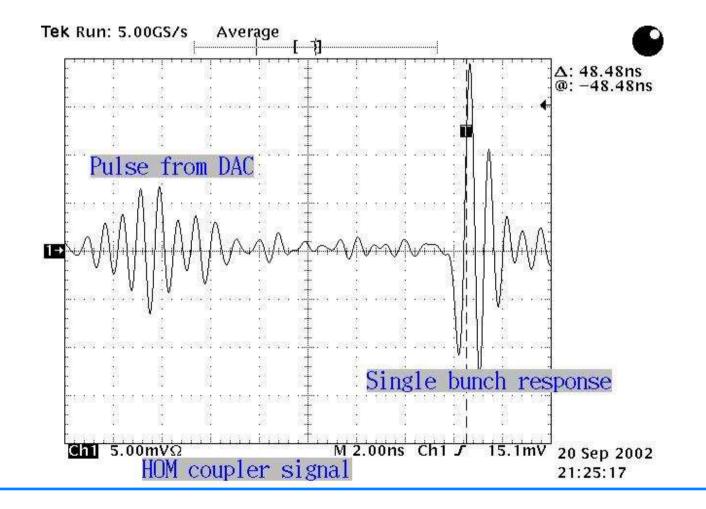

## Beam response

**Typical signal trace**

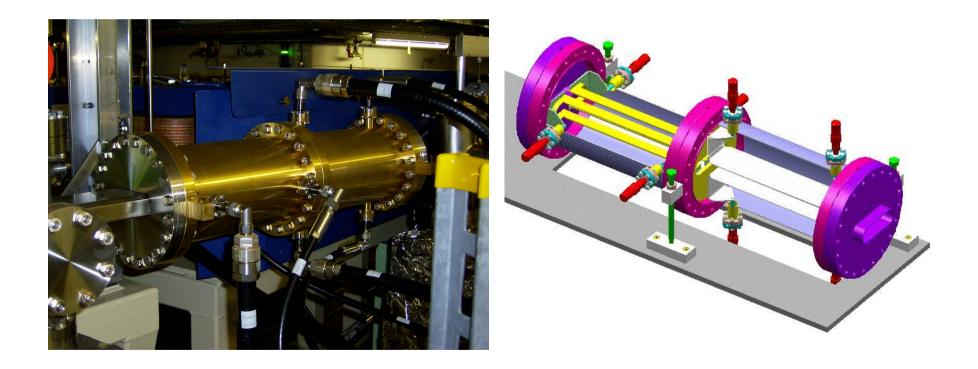

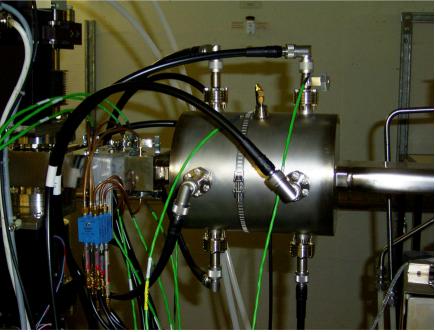

### **Transverse kickers**

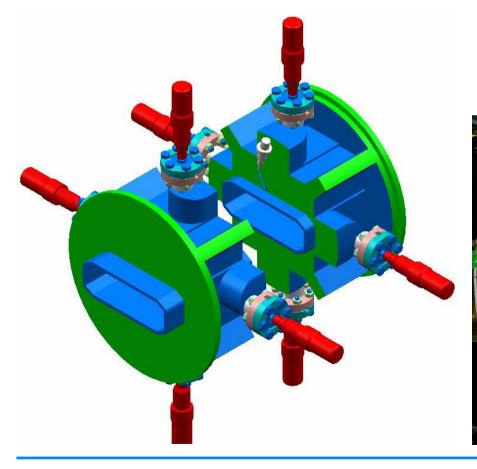

## Longitudinal kicker

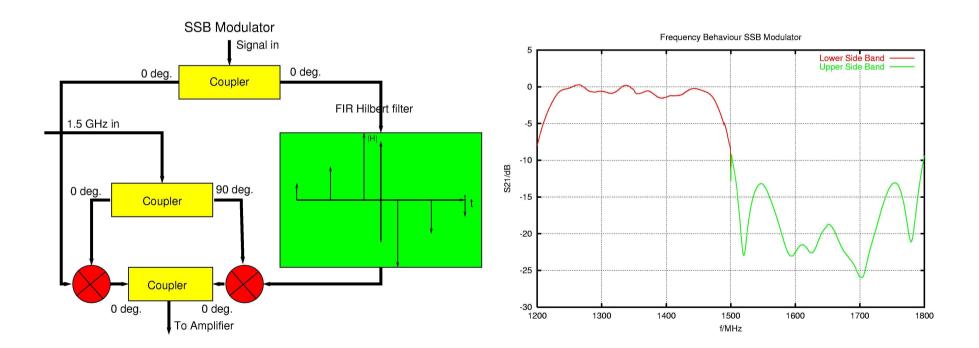

#### SSB modulator for longitudinal plane (Others use QPSK?)

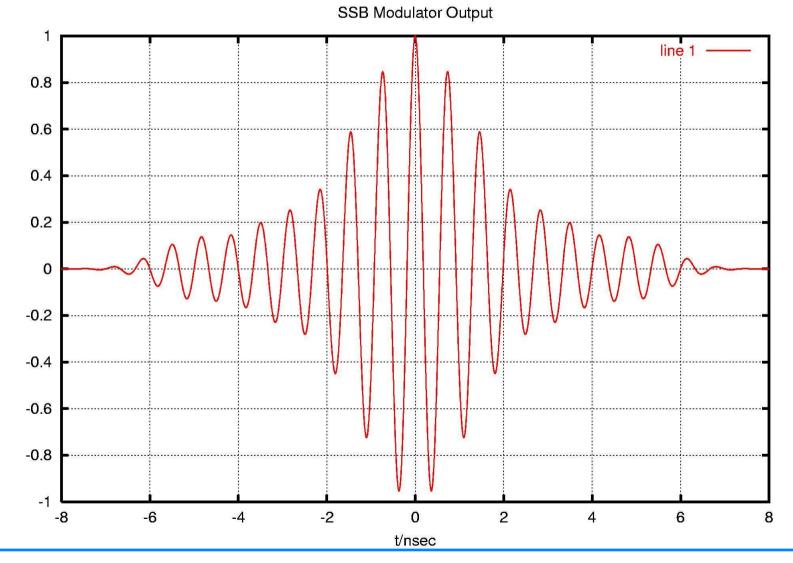

## Pulse response: SSB + Filter + Kicker

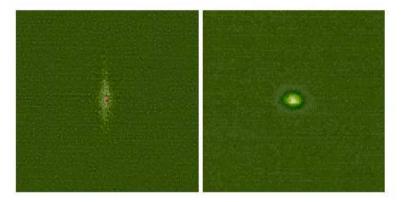

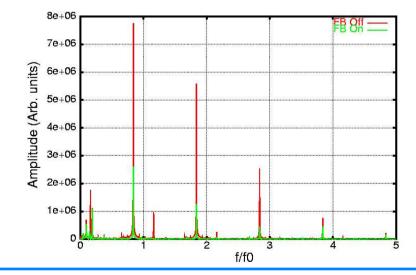

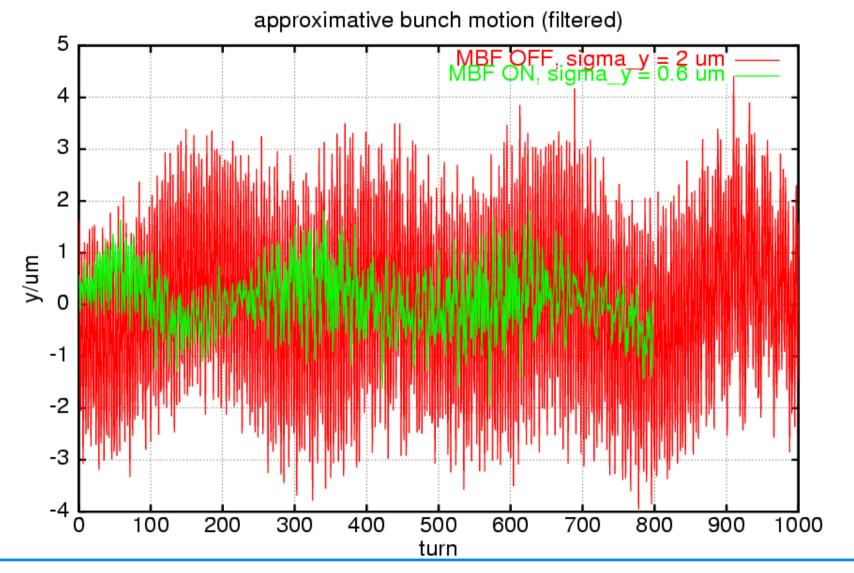

#### Boring, but true: Early performance of bunch by bunch feedback

MBF off

MBF on

BUT

No more

ADC & DAC boards

## Specs for in house ADC/DAC development

| Sampling Rate                   | 200-500 MHz                               |

|---------------------------------|-------------------------------------------|

| Resolution                      | 8 bits                                    |

| Input Impedance                 | 50 Ω                                      |

| Coupling                        | AC                                        |

| Analog Bandwidth (3 dB)         | 5kHz - 500 MHz                            |

| In-band Phase Rotation          | $< 10^{o}$                                |

| Input Level(ADC)                | 0 dBm                                     |

| Output Level(DAC)               | 6 dBm                                     |

| Signal/Noise + Distortion Ratio |                                           |

| (Total Dynamic Distortion)      | > 40dB                                    |

| External Clock                  | Sine Wave/DECL                            |

| Clock Programmable Shift        | Range $> 2$ ns, steps $< 100$ ps          |

| External Trigger                | DECL                                      |

| Total Jitter from               |                                           |

| Clock Input to Analog I/O:      | < 10 ps                                   |

| VME interface                   | VME64x compatible A32/D32 (base           |

|                                 | address geographic) or switch selectable) |

| FPDP Interface                  | ANSI/VITA 17 Single Ended TTL,            |

|                                 | 80 pin connector                          |

| Number of FPDP Ports            | 1 to 12                                   |

| Memory Size                     | 8 MByte                                   |

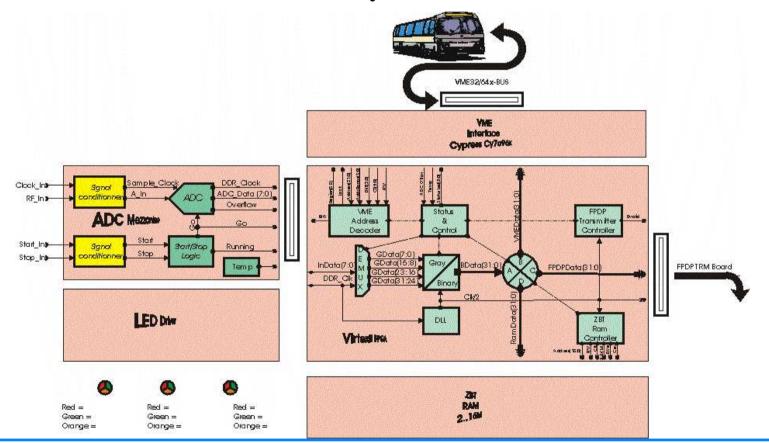

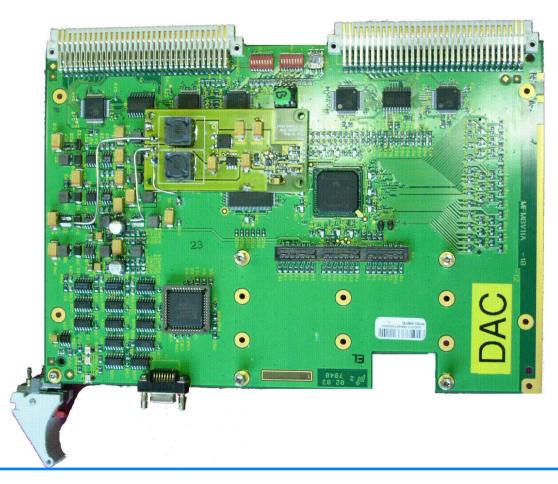

Sandwich structure with three layers:

- Mezzanine boards with ADC or DAC

- Main board with VME interface, Virtex FPGA and RAM (common design for ADC and DAC)

- (common design for MDC and DMC)

- FPDP board with second (de-)multiplexer stage

(common for ADC and DAC)

(For multiplexing ratios greater six:

fourth board carrying additional FPDP connectors)

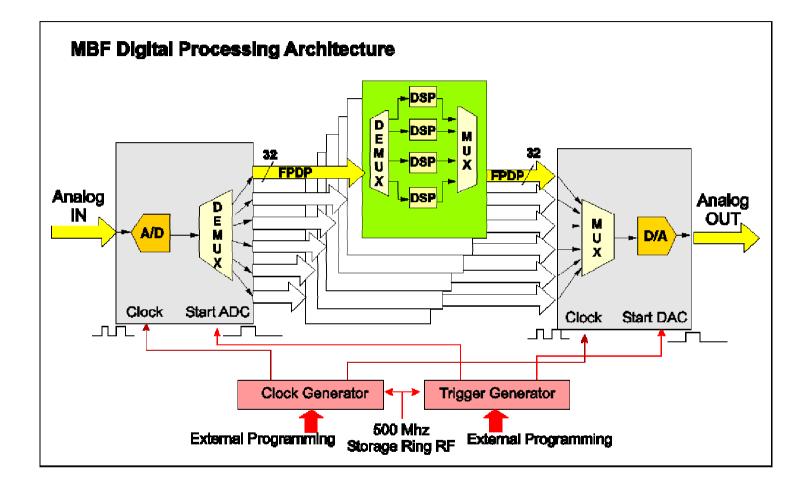

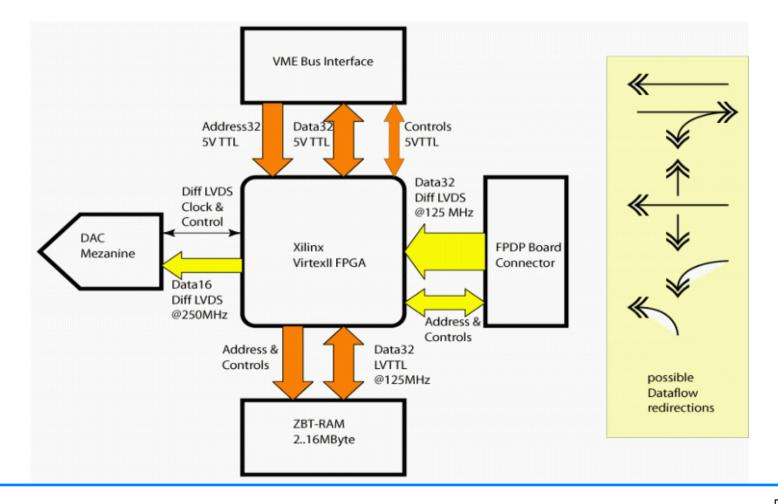

## **Functional blocks**

**Basic Layout ADC**

#### Main board

#### Main complexity hidden within FPGA firmware

## **Options for data flux**

### **Closed loop**

For long time had problems with non reproducible settings for ADC/DAC latency (hopefully resolved by now)

Transverse system 95% complete

## Status from the user perspective

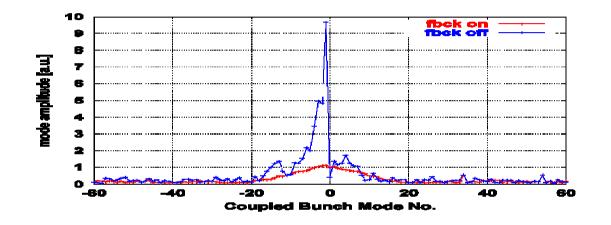

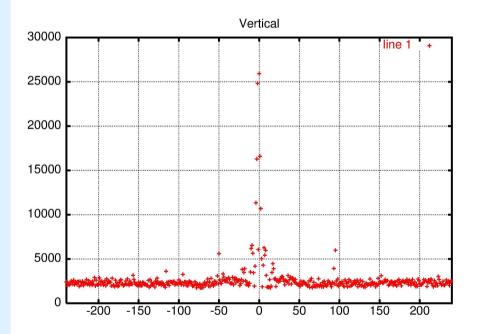

#### Vertical plane:

Slight instabilities, not visible for users (but they are getting more sophisticated ...)

Horizontal plane:

Stable. FB may help to close bump of injection kickers (Top up!)

Longitudinal plane:

Stable. Fallback, if 3 HC cavity gets in normal conducting state (Otherwise Ibeam <180 mA).

General:

More freedom in settings (Chromaticity)

Fill pattern feedback?

Typical CBM spectrum during user operation